26.12.20.000 Утверждён ИМЕС.467444.152РЭ-ЛУ

# МОДУЛИ ВВОДА-ВЫВОДА DIC552, DIC553

Руководство по эксплуатации ИМЕС.467444.152РЭ

# Список обновлений и дополнений к документу

| № обновления | Краткое описание изменений                                                                                                                                                                                              | Наименование<br>изделия | Дата         |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------|

| 1.0          | Начальная версия                                                                                                                                                                                                        | DIC552, DIC553          | Май 2022     |

| 1.1          | Откорректировано обозначение модулей при заказе, добавлено Приложение А.                                                                                                                                                | DIC552, DIC553          | Август 2022  |

| 1.2          | В соответствии с протоколами расчета надежности откорректированы значения МТВГ в таблице 1 раздела 1.2. Откорректировано содержание, разделы 2.2, 3.1.1, в таблицу 3 раздела 1.4 добавлена информация об опции -COATED. | DIC552, DIC553          | Октябрь 2022 |

| 1.3          | Внесены исполнения с<br>влагозащитным покрытием DIC552-01-<br>COATED, DIC553-01-COATED (ранее<br>была опция)                                                                                                            | DIC552, DIC553          | Май 2024     |

# Содержание

| Обозна | ачения                                       | 6  |

|--------|----------------------------------------------|----|

| Требов | вания безопасности                           | 7  |

| Общиє  | е правила использования изделий              | 8  |

| 1      | Описание и работа                            | 9  |

| 1.1    | Назначение                                   | 9  |

| 1.2    | Технические характеристики                   | 9  |

| 1.3    | Условия эксплуатации                         | 11 |

| 1.4    | Варианты исполнения                          | 12 |

| 1.5    | Комплект поставки                            | 12 |

| 1.6    | Требования по безопасности                   | 13 |

| 1.7    | Маркировка                                   | 13 |

| 1.8    | Упаковка                                     | 14 |

| 2      | Устройство и работа модуля                   | 15 |

| 2.1    | Структурная схема                            | 15 |

| 2.2    | Описание мезонинов                           | 17 |

| 2.2.1  | Мезонин цифрового ввода-вывода MIC1003-03    | 18 |

| 2.2.2  | Мезонин интерфейсов ИРПС MIC1004             | 20 |

| 2.2.3  | Мезонин интерфейса МКИО MIC1007-01           | 22 |

| 2.2.4  | Мезонин интерфейса CAN MIC1010-01            | 23 |

| 2.2.5  | Мезонин интерфейсов RS485/422/232 MIC1011-01 | 25 |

| 2.2.6  | Мезонин интерфейса ПК MIC1012-0X             | 27 |

| 2.2.7  | Описание разъемов мезонинов и портов модуля  | 28 |

| 2.2.8  | Описание интерфейсов связи с мезонинами      | 30 |

| 2.3    | Карта памяти модуля                          | 32 |

| 2.3.1  | Регистровая модель пространства ввода-вывода | 36 |

| 3      | Использование по назначению                  | 56 |

| 3.1    | Подготовка изделия к использованию           | 56 |

| 3.1.1  | Установка драйвера                           | 56 |

| 3.1.2  | Информация о видах опасных воздействий       | 56 |

| 3.1.3  | Общие требования                             | 56 |

| 3.1.4  | Требование электростатической безопасности | 57 |

|--------|--------------------------------------------|----|

| 3.2    | Использование изделия                      | 57 |

| 3.3    | Техническое обслуживание                   | 57 |

| 3.4    | Ремонт                                     | 57 |

| 4      | Транспортирование, распаковка, хранение    | 58 |

| 4.1    | Транспортирование                          | 58 |

| 4.2    | Распаковка                                 | 58 |

| 4.3    | Хранение                                   | 58 |

| Прилож | кение А                                    | 59 |

(далее руководство) Настоящее руководство ПО эксплуатации предназначено для ознакомления с устройством, принципом работы и основными сведениями, необходимыми для ввода в эксплуатацию, использования ПО назначению И обслуживания изделий: «Модуль ввода-вывода DIC552», «Модуль ввода-вывода DIC553».

#### Обозначения

## Осторожно, электрическое напряжение!

Этот знак и надпись предупреждают об опасностях, связанных с электрическими разрядами (> 60 В) при прикосновении к изделию или к его частям. Несоблюдение мер предосторожности, упомянутых или предписанных правилами, может подвергнуть опасности Вашу жизнь или здоровье, а также может привести к повреждению изделия.

#### ВНИМАНИЕ!

**Изделие, чувствительное к воздействию** статического электричества!

Этот знак и надпись сообщают о том, что изделие и его компоненты чувствительны К статическому электричеству, поэтому следует проявлять осторожность при обращении с ними и при проведении чтобы гарантировать проверок, целостность работоспособность. См. также раздел, посвященный инструкциям по обращению с изделием и распаковке, приведенный ниже.

#### ВНИМАНИЕ!

Этот знак призван обратить Ваше внимание на те аспекты Руководства, неполное понимание или игнорирование которых может подвергнуть опасности Ваше здоровье или привести к повреждению изделия.

#### Примечание

Этим знаком отмечены фрагменты текста, которые следует внимательно прочитать.

# Требования безопасности

Данные изделия ЗАО «НПФ «ДОЛОМАНТ» разработаны и испытаны с целью обеспечения соответствия требованиям электрической безопасности. Их конструкция предусматривает длительную безотказную работу. Срок службы изделий может значительно сократиться из-за неправильного обращения с ними при распаковке и установке. Таким образом, в интересах Вашей безопасности и для обеспечения правильной работы изделий Вам следует придерживаться приведенных ниже рекомендаций.

# Правила безопасного обращения с электрическим напряжением

#### ВНИМАНИЕ!

Все работы с данными изделиями должны выполняться только персоналом с достаточной для этого квалификацией.

## Осторожно, электрическое напряжение!

Перед установкой изделий, а также при подключении внешнего оборудования убедитесь в том, что сетевое питание отключено. Это относится также и к установке плат расширения.

В процессе установки, ремонта и обслуживания изделий существует серьезная опасность поражения электрическим током, поэтому всегда вынимайте из розетки шнур питания во время проведения работ. Это относится также и к другим подводящим питание кабелям.

# Инструкции по обращению с изделиями

# Изделия, чувствительные к воздействию статического электричества!

Изделия и их компоненты чувствительны к воздействию статического электричества. Поэтому для обеспечения сохранности и работоспособности при обращении с ними требуется особое внимание.

Не оставляйте изделия без защитной упаковки в нерабочем положении.

По возможности всегда работайте на рабочих местах с защитой от статического электричества. Если это невозможно, то пользователю необходимо снять с себя статический заряд перед тем, как прикасаться к изделиям руками или инструментом. Это удобнее всего сделать, прикоснувшись к металлической части корпуса системы.

# Общие правила использования изделий

Для сохранения гарантии изделия не должны подвергаться никаким переделкам Любые несанкционированные изменениям. компанией 3A0 «НПФ «ДОЛОМАНТ» изменения усовершенствования, И кроме приведенных в настоящем Руководстве или полученных от службы технической поддержки ЗАО «НПФ «ДОЛОМАНТ» в виде набора инструкций по их выполнению, аннулируют гарантию.

Эти изделия должны устанавливаться и подключаться только к системам, отвечающим всем необходимым техническим и климатическим требованиям. Это относится и к диапазону рабочих температур изделий. Также следует учитывать температурные ограничения батарей, установленных на плате.

Выполняя все необходимые операции по установке и настройке, следуйте инструкциям только этого Руководства.

Сохраняйте оригинальную упаковку для хранения изделий в будущем или для транспортировки в гарантийном случае. В случае необходимости транспортировать или хранить изделие упакуйте его так же, как оно было упаковано при получении.

Проявляйте особую осторожность при распаковке и обращении с изделием. Действуйте в соответствии с инструкциями раздела 4.2 Распаковка.

Не допускается подключение внешнего оборудования, кабелей коммуникационных интерфейсов без отключения питания изделия и подключаемого внешнего оборудования.

# 1 Описание и работа

#### 1.1 Назначение

DIC552 ИМЕС.467444.152 **DIC553** Модули ввода-вывода ИМЕС.467444.153 (далее модуль/модули) – универсальные модули вводавывода информации для работы на шине CompactPCI®. Модули создаются по мезонинной технологии и являются носителями с возможностью установки мезонинов с лицевым выводом. Функциональные возможности модулей определяют установленные мезонины (например: МІС1003-03, МІС1004-01, MIC1007-01, MIC1010-01, MIC1011-01, MIC1012-0X). Модули предназначены для использования в системах управления реального времени, контроля производства, сбора данных и т.п.

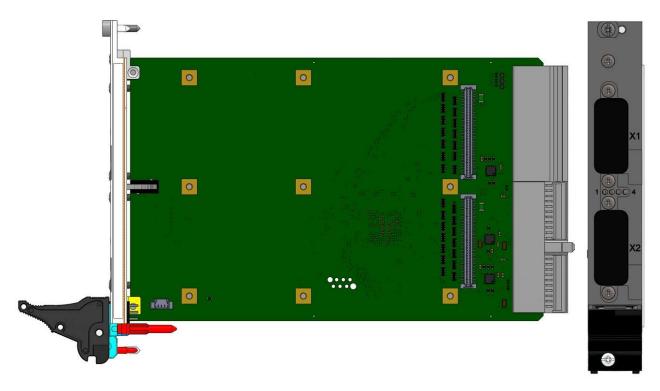

DIC552 — носитель мезонинов выполнен в стандарте CompactPCI® и обеспечивает размещение в конструктивах типа 3U. Модуль позволяет установить на себя до двух мезонинных плат стандартного размера.

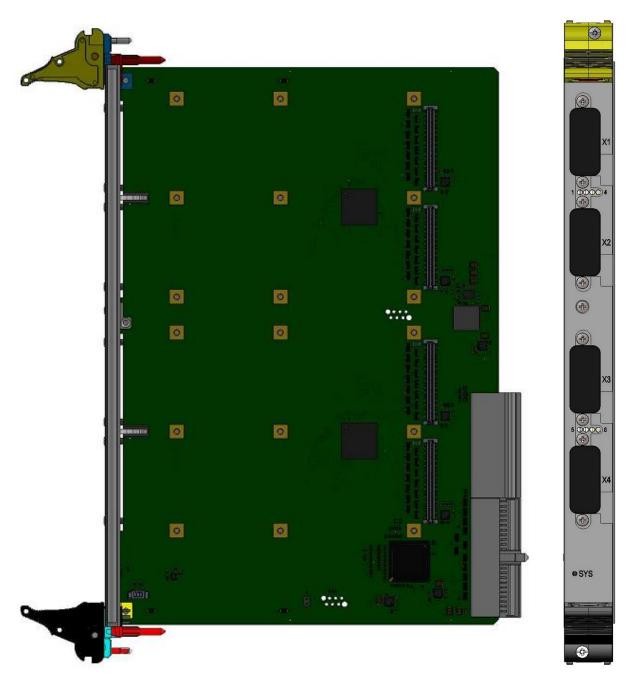

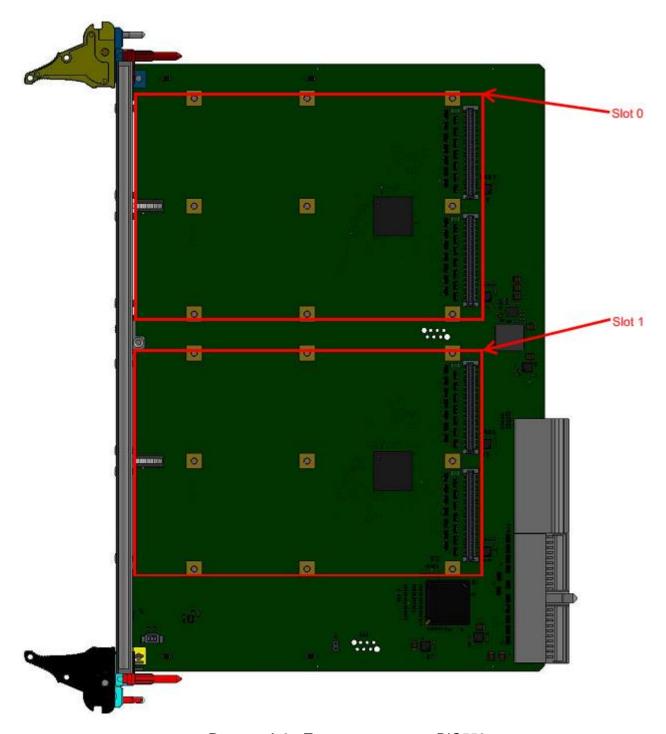

DIC553 — носитель мезонинов выполнен в стандарте CompactPCI® и обеспечивает размещение в конструктивах типа 6U. Модуль позволяет установить на себя до четырех мезонинных плат стандартного размера.

Мезонины представляют собой функционально завершенные платы, обеспечивающие аналоговый или цифровой ввод/вывод. Исполнение мезонина не зависит от используемой системной шины компьютера, общение мезонина с модулем происходит с использованием последовательных и параллельных каналов связи (SPI, SPORT, UART и др.). Связь системной шины и каналов связи обеспечивает модуль-носитель.

Внешний вид модулей показан в приложении А.

# 1.2 Технические характеристики

Технические характеристики указаны в таблице 1.

Таблица 1 - Технические характеристики модуля

| Параметр    | Модуль ввода-вывода<br>DIC552 | Модуль ввода-вывода<br>DIC553 |

|-------------|-------------------------------|-------------------------------|

| System BUS  | CompactPCI 32-бита,<br>33 МГц | CompactPCI 32-бита,<br>33 МГц |

| Конструктив | 3U                            | 6U                            |

| Параметр                                             |                | Модуль ввода-вывода<br>DIC552                                              | Модуль ввода-вывода<br>DIC553                                           |  |

|------------------------------------------------------|----------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------|--|

| Интерфейс с мезониног<br>размера                     | м стандартного | SPI –<br>UART 1655<br>Параллельный пој<br>SPORT<br>Таймер 82<br>Шина 32-би | · шт.;<br>)А – 4 шт.;<br>т (16-бит) – 3 шт.;<br>- 4 шт.;<br>i4 – 2 шт.; |  |

| Поддержка мезонинов<br>размера, шт                   | стандартного   | 2                                                                          | 4                                                                       |  |

| Напряжение питания cooтветствии c CompactP           |                | +12, +3,3                                                                  | +12, +5, +3,3                                                           |  |

| Мощность без учета потребления мезонинов (макс.), Вт |                | 6                                                                          | 12                                                                      |  |

| Мощность потребления мезонинов по +12В               | общее          | 12                                                                         | 12                                                                      |  |

| (макс.), Вт                                          | один мезонин   | 12                                                                         | 12                                                                      |  |

| Мощность потребления мезонинов по +3.3В              | общее          | 15                                                                         | 20                                                                      |  |

| (макс.), Вт                                          | один мезонин   | 4,5                                                                        | 4,5                                                                     |  |

| Мощность потребления                                 | общее          |                                                                            | 24                                                                      |  |

| мезонинов по +5В<br>(макс.), Вт                      | один мезонин   | -                                                                          | 12                                                                      |  |

| MTBF, ч                                              |                | 1000000                                                                    | 500000                                                                  |  |

| Габаритные размеры, мм                               |                | 131x214x21                                                                 | 214x267x21                                                              |  |

| Масса модуля, не более, кг                           |                | 0,2                                                                        | 0,4                                                                     |  |

#### Примечания

#### Функциональные возможности:

- интерфейс с системной шиной CompactPCI 32-бит, 33 МГц.

- интерфейсы доступные на мультиплексированной шине для каждого мезонина:

- 4 SPI интерфейса с максимальной длиной слова 32 бита и частотой тактирования до 32 МГц;

- 4 UART интерфейса (скорость передачи до 1 Мбод);

- 4 SPORT последовательные интерфейсы с максимальной длиной слова 32 бита и частотой тактирования до 32 МГц, а также поддержкой TDMA и I2S режимов;

<sup>1</sup> Для DIC553 мезонины, потребляющих больше 12 Вт на слот (по +12 В), необходимо устанавливать в один из разъемов Slot 0 (рисунок А.3)

<sup>2</sup> Значения MTBF рассчитаны по модели вычислений Telcordia Issue 1 (методика расчета Method I Case 3) для непрерывной эксплуатации при наземном размещении в условиях, соответствующих климатическому исполнению УХЛ4 по ГОСТ 15150-69, при температуре окружающей среды плюс  $30\ ^{\circ}$ C.

- 2 16-разрядных параллельных порта с возможностью генерации одиночных выходных импульсов (время доступа определяется циклом шины PCI) (без генерации прерываний);

- 1 16-разрядный параллельный порт с возможностью генерации прерываний при изменении состояния выводов порта (время доступа определяется циклом шины PCI);

- 32-разрядная шина, совместимая с Wishbone, с тактовой частотой 32 МГц;

- интерфейс для идентификации мезонина (SPI);

- 2 счетчика-таймера, совместимых с 8254, с тактовой частотой 20 МГц;

- поддержка DMA на шине CompactPCI.

## Программная совместимость:

■ Драйверная поддержка для ОС Linux (с ядром не ниже v.3.19). Драйверы и набор программных библиотек совместим с ПО от DIC551.

# 1.3 Условия эксплуатации

Условия эксплуатации указаны в таблице 2.

Таблица 2 - Условия эксплуатации

| Вид                | Наименование               | Значение параметра Докум |                     | Документ                          |  |

|--------------------|----------------------------|--------------------------|---------------------|-----------------------------------|--|

| воздействия        | параметра                  | DIC552                   | DIC552 DIC553       |                                   |  |

| Смена              | Низкая температура         | - 40 °C                  | - 40 °C             | ГОСТ 28209-89                     |  |

| температур         | Высокая температура        | + 85 °C                  | + 85 °C             | (МЭК 68-2-14-84)<br>Испытание Nb  |  |

| Влажное тепло*     | Относительная<br>влажность | (55±2) °C<br>93±3 %      | (55±2) °C<br>93±3 % | ГОСТ 28216-89<br>(МЭК 68-2-30-82) |  |

| Синусоидальная     | Диапазон частот (Гц)       | 10500                    | 10500               | ГОСТ 28203-89                     |  |

| вибрация           | Ускорение, g               | 5                        | 2                   | (MЭK 68-2-6-82)                   |  |

| Одиночные<br>удары | Пиковое ускорение, д       | 100                      | 50                  | ГОСТ 28213-89<br>(МЭК 68-2-27-87) |  |

| Многократные       | Пиковое ускорение, д       | 50                       | 30                  | ΓΟCT 28215-89                     |  |

| удары              | Количество ударов          | 1000                     | 1000                | (MЭК 68-2-29-87)                  |  |

# 1.4 Варианты исполнения

Варианты исполнения модуля приведены в таблице 3.

Таблица 3 - Варианты исполнения

| Наименование               | Обозначение при заказе |

|----------------------------|------------------------|

| Модуль ввода-вывода DIC552 | DIC552-01              |

| МОДУЛЬ ВВОДА-ВЫВОДА БІСОО2 | DIC552-01-COATED       |

| Manyar propagation DICES   | DIC553-01              |

| Модуль ввода-вывода DIC553 | DIC553-01-COATED       |

# 1.5 Комплект поставки

Комплект поставки модуля DIC552 приведен в таблице 4.

Таблица 4 - Комплект поставки модуля DIC552

| Обозначение                           | Наименование                                                                                                                             | Коли-<br>чество | Приме-<br>чание         |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------|

| ИМЕС.467444.152<br>ИМЕС.467444.152-01 | Модуль ввода-вывода DIC552<br>Модуль ввода-вывода DIC552-01-COATED                                                                       | 1 шт.           |                         |

| ИМЕС.467369.045                       | Компакт-диск с руководством по<br>эксплуатации и программным<br>обеспечением                                                             | 1 шт.           |                         |

| ИМЕС.468911.002                       | Комплект монтажных частей в составе: - шайба ИМЕС.741124.076 – 3 шт.; - упор ИМЕС.741521.001 – 6 шт.; - винт A2.M2,5-6gx8.56.016 – 9 шт. |                 |                         |

| ИМЕС.467929.001                       | Комплект наклеек                                                                                                                         | 2 шт.           |                         |

| ИМЕС.421945.065-03                    | 065-03 Упаковка                                                                                                                          |                 |                         |

|                                       | Эксплуатационная документация                                                                                                            |                 |                         |

| ИМЕС.467444.152ПС                     | Модуль ввода-вывода DIC552. Паспорт                                                                                                      | 1 шт.           |                         |

| ИМЕС.467444.152РЭ                     | Модуль ввода-вывода DIC552.<br>Руководство по эксплуатации                                                                               | 1 шт.           | На<br>компакт-<br>диске |

Комплект поставки модуля DIC553 приведен в таблице 5.

Таблица 5 - Комплект поставки модуля DIC553

| Обозначение                                                                                                                              | Наименование                                                              | Коли-<br>чество | Приме-<br>чание         |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------|-------------------------|

| ИМЕС.467444.153<br>ИМЕС.467444.153-01                                                                                                    | Модуль ввода-вывода DIC553<br>Модуль ввода-вывода DIC553-01-COATED        | 1 шт.           |                         |

| ИМЕС.467369.045                                                                                                                          | Компакт-диск с руководством по<br>эксплуатации и программным обеспечением | 1 шт.           |                         |

| Комплект монтажных частей в составе: - шайба ИМЕС.741124.076 – 3 шт.; - упор ИМЕС.741521.001 – 6 шт.; - винт A2.M2,5-6gx8.56.016 – 9 шт. |                                                                           | 2 шт.           |                         |

| ИМЕС.467929.001                                                                                                                          | Комплект наклеек                                                          | 4 шт.           |                         |

| ИМЕС.421945.071-16                                                                                                                       | Упаковка                                                                  | 1 шт.           |                         |

|                                                                                                                                          | Эксплуатационная документация                                             |                 |                         |

| ИМЕС.467444.153ПС Модуль ввода-вывода DIC553. Паспорт                                                                                    |                                                                           | 1 шт.           |                         |

| ИМЕС.467444.153РЭ                                                                                                                        | Молупь ввола-вывола DIC553. Руковолство                                   |                 | На<br>компакт-<br>диске |

# 1.6 Требования по безопасности

Изделие должно соответствовать общим требованиям безопасности для оборудования информационных технологий по ГОСТ Р МЭК 60950-2002 (для оборудования, подключаемого к электросети напряжением до 600 В).

Конструкция изделия должна обеспечивать безопасность обслуживающего персонала в соответствии с требованиями по безопасности ГОСТ 12.2.056-81.

# 1.7 Маркировка

Изделие должно иметь маркировку, расположенную согласно сборочным чертежам ИМЕС.467444.152СБ (DIC552) и ИМЕС.467444.153СБ (DIC553).

Маркировка изделия должна содержать:

- сокращенное наименование (шифр) изделия;

- товарный знак завода-изготовителя;

- заводской номер изделия.

Маркировка упаковки должна содержать:

- сокращенное наименование (шифр) изделия;

- товарный знак завода-изготовителя;

- штрих-код;

- страну изготовления.

#### 1.8 Упаковка

Модуль упаковывается в отдельную упаковку предприятия-изготовителя: антистатический пакет и картонную коробку размерами 230х155х45 мм (DIC552) или 350х260х70 мм (DIC553).

Таблица 6 – Масса модуля в упаковке

| Наименование               | Масса модуля в упаковке, кг, не более |

|----------------------------|---------------------------------------|

| Модуль ввода-вывода DIC552 | 0,3                                   |

| Модуль ввода-вывода DIC553 | 0,5                                   |

# 2 Устройство и работа модуля

# 2.1 Структурная схема

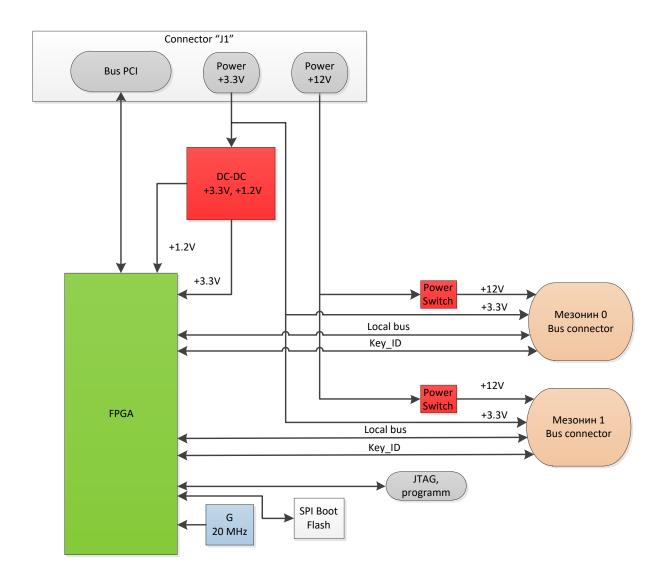

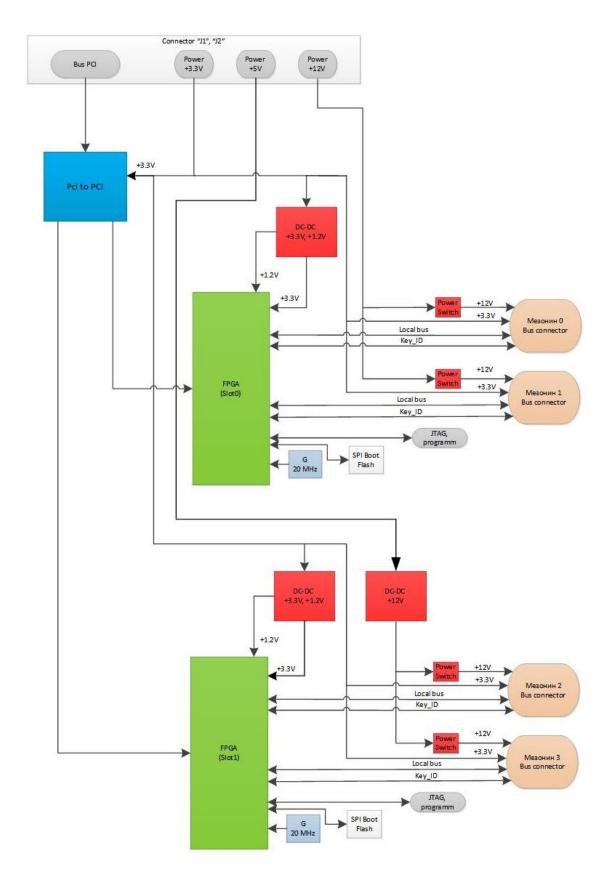

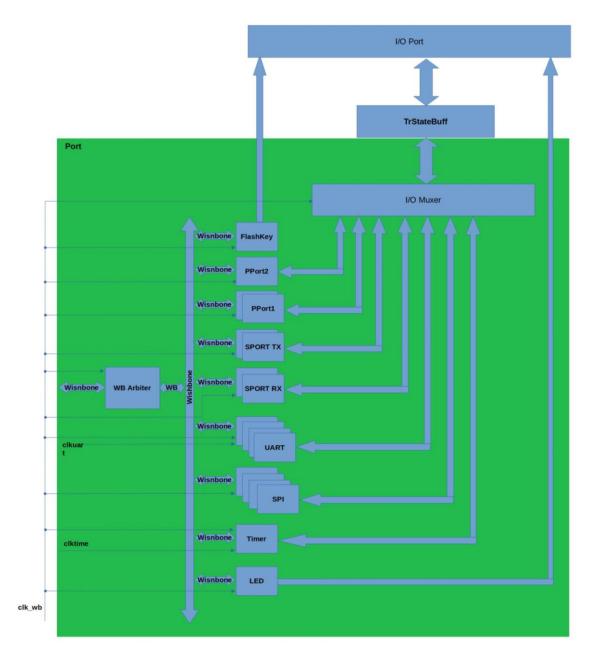

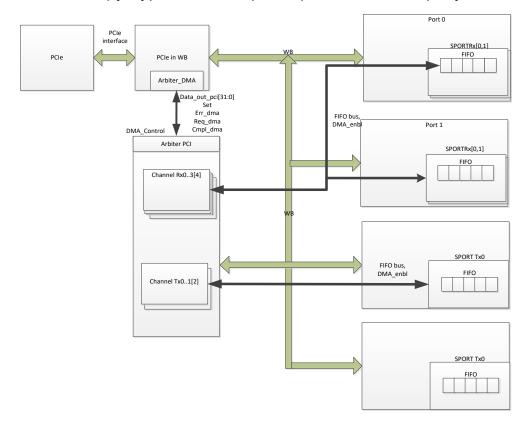

На рисунках 1 и 2 и приведены структурные схемы модулей DIC552 и DIC553.

Модуль обеспечивает передачу данных между шиной PCI и мезонинами, питание мезонинов с функциями защиты от перегрузки по току, горячую замену модуля (Hot Swap).

Рисунок 1 - Структурная схема модуля DIC552 (3U)

Рисунок 2 - Структурная схема модуля DIC553 (6U)

На FPGA реализуется интерфейс обмена по шине PCI и функционал управления мезонинами, также FPGA контролирует и управляет питанием мезонинов. Питание мезонинов осуществляется напряжениями +3.3 В и +12 В. Для управления питанием +12 В каждого мезонина применяются интеллектуальные ключи с возможностью защиты по току (Power Switch). На каждый мезонин поступает также дополнительное, маломощное питание +3.3 В, используемое для питания идентификационной памяти мезонина. Для подключения мезонинов используются 64 контактные межплатные разъемы.

Каждый мезонин соединен с модулем мультиплексированной шиной, содержащей следующие интерфейсы: SPORT (4 канала), SPI (4 канала), UART (тип 16550A, 4 канала), параллельный порт 16 бит (3 канала), 32 разрядная шина Wishbone.

Одновременно на модуле доступны все интерфейсы, но в связи с ограничением числа контактов на разъемах мезонина, каждый (с 9 по 56) вывод разъема для подключения мезонина может быть подключен к одному из 4 интерфейсов (см. раздел 2.2.7). Настройка функции каждого вывода индивидуальна и определяется регистром «Регистр установки принадлежности выводов FPGA устройствам» параллельного порта.

Отличие DIC553 (6U конструктив) от DIC552 (3U конструктив) – наличие моста PCI-to-PCI и дублирования схемы носителя мезонинов. Таким образом, 3U модуль поддерживает подключение двух мезонинов, а 6U модуль – четырех. 6U модуль представляет собой два независимых модуля носителя мезонинов, выполненные на одной плате. Конфигурации каждой FPGA на модуле DIC553 идентичны конфигурации FPGA на DIC552.

В качестве моста PCI-to-PCI используется мост PI7C8150BNDIE (ф. Diodes Incorporated).

#### 2.2 Описание мезонинов

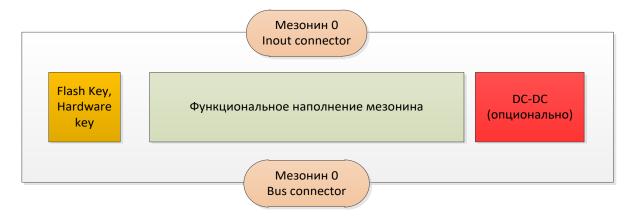

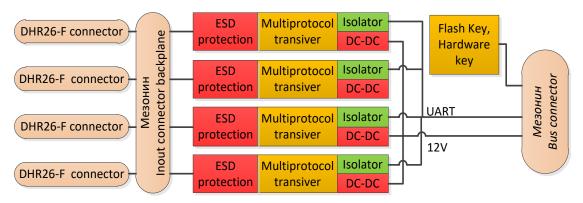

На рисунке 3 представлена обобщенная структурная схема мезонина. Мезонин представляет собой плату, устанавливаемую на модуль. Работа с мезонином со стороны компьютера осуществляется через комбинацию интерфейсов, предоставляемых модулем. На модуле, кроме функционального наполнения мезонина, располагаются идентификационные средства, такие как:

hard key – аппаратный ключ, служащий для идентификации наличия мезонина;

flash key — микросхема памяти с последовательным интерфейсом.

Содержит информацию о модуле, типе используемых протоколов, настройках мезонина и т.д., требуется для автоматической настройки драйвера модуля.

Мезонин устанавливается на высоте 10,5 мм от модуля. На один DIC552 может устанавливаться до двух мезонинов стандартного размера или один мезонин двойного размера. На один DIC553 может устанавливаться до четырех мезонинов стандартного размера или два мезонина двойного размера.

Рисунок 3 - Обобщенная структурная схема мезонина

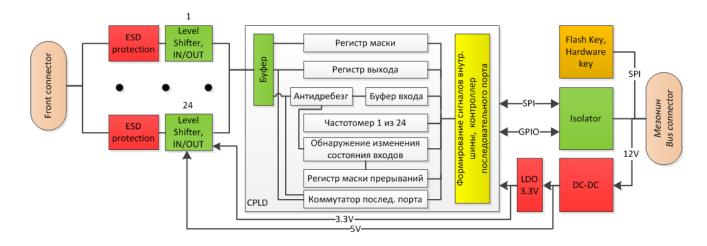

# 2.2.1 Мезонин цифрового ввода-вывода МІС1003-03

Основные особенности:

- 24 канала цифрового ввода вывода с индивидуальной настройкой направления;

- групповая гальваническая изоляция каналов 750 В;

- защита выходных сигналов от электростатического разряда;

- выдача и прием последовательного кода (совместимого с RS232 по протоколу) по любому каналу;

- формирование прерываний при изменении данных на входах;

- измерение частоты (до 2000 кГц) сигналов по любому каналу;

- программируемый интервал времени устранения дребезга для входов (антидребезг);

- питание мезонина: от модуля;

- мощность: не более 4 Вт.

Мезонин предназначен для ввода/вывода 24 сигналов с логическими уровнями CMOS 5 В и содержит защиту от статического электричества. В группе выходные данные на контактах меняются одновременно, задержка изменения данных (latency time) составляет не более 2,1 мкс. Может применяться для измерения частоты сигналов, приема и выдачи последовательного кода,

преобразования кодов, управления алфавитно-цифровыми индикаторами, формирования временных диаграмм управления.

Мезонин MIC1003-03 имеет фронтальный вывод сигналов через разъем типа DSUB26.

Требования к внешней нагрузке модуля: нагрузка на один выход не более 25 мА, максимальная общая нагрузка модуля на выход не более 400 мА.

На рисунке 4 показана обобщенная структурная схема мезонина.

Рисунок 4 - Структурная схема мезонина МІС1003-03

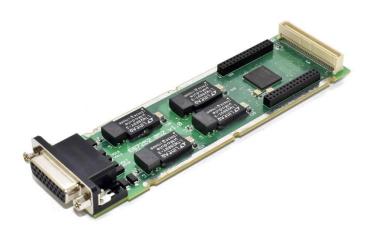

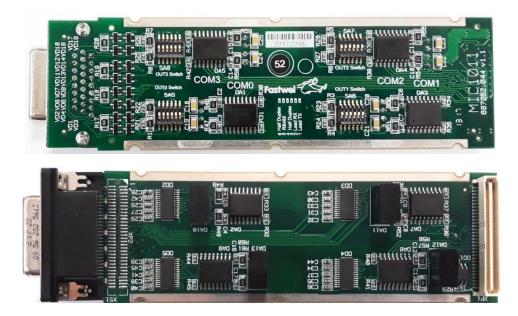

На рисунке 5 показан внешний вид мезонина.

Рисунок 5 - Внешний вид мезонина МІС1003-03

# 2.2.2 Мезонин интерфейсов ИРПС МІС1004

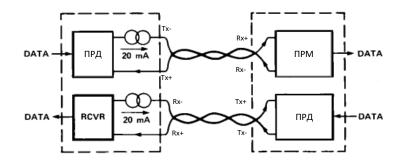

Обобщенная структура МІС1004 показана на рисунке 6.

Рисунок 6 - Структурная схема мезонина МІС1004-01

#### Основные особенности:

- 4 канала портов ИРПС;

- гальваническая изоляция каналов 750 В;

- защита выходных сигналов от электростатического разряда;

- возможность отключения питания каждого порта индивидуально;

- работа на 2-х и 4-х проводные линии;

- работа в режиме Master-Slave;

- выходной разъем мезонина DHR26F;

- питание: от модуля;

- мощность: не более 5 Вт.

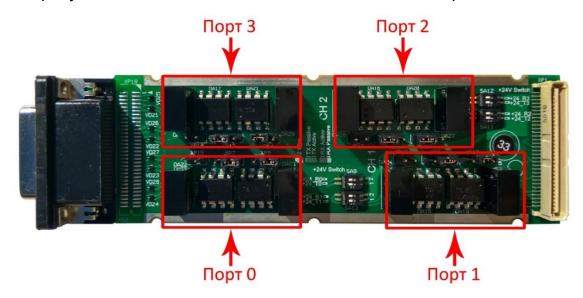

На рисунке 7 показан внешний вид МІС1004-01 со стороны ТОР.

Рисунок 7 - Внешний вид модуля МІС1004-01 со стороны ТОР

Мезонин предназначен для осуществления операций ввода/вывода через 4 индивидуально гальванически изолированных последовательных порта типа ИРПС и представляет собой плату преобразования уровней сигнала от UART, расположенного на модуле, в уровни сигналов, соответствующих стандарту ИРПС. Переключение портов типа master-slave и 2x-4x проводная линия связи производиться с помощью перемычек и микропереключателей. Комбинация перемычек задает тип передатчика и приемника, по наличию источника тока в цепи: активный или пассивный. С помощью перемычек замыкаются соответствующие порту сигнальные линии Тх- и Rx+ для полудуплексного режима.

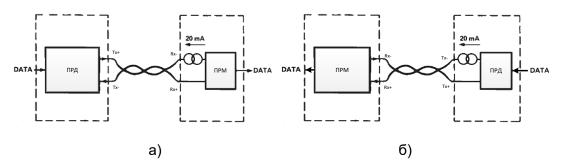

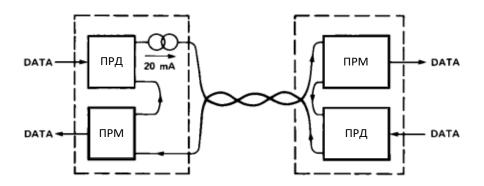

Передача данных между устройствами возможна в 3-х возможных конфигурациях порта: однонаправленная, полудуплексная или полнодуплексная передача/прием в активном или пассивном режимах. На рисунках 8 - 10 соответственно показаны варианты подключения.

Рисунок 8 - Однонаправленное подключение: а) активный приемник; б) активный передатчик

Рисунок 9 - Полудуплексное подключение

Рисунок 10 - Полнодуплексное подключение

# 2.2.3 Мезонин интерфейса МКИО МІС1007-01

Основные технические характеристики:

- поддержка протокола:

- поддержка двух резервируемых каналов связи или четырех независимых каналов (без резервирования);

- работа в режимах контроллера шины, оконечного устройства и монитора шины;

- возможность трансформаторного и прямого подключений к линии;

- скорость передачи информационных данных 1 Мбит/с;

- система команд согласно ГОСТ Р 52070-2003;

- гальваническая изоляция каналов: 750 В;

- программная совместимость с ОС: Linux, QNX;

- выходной разъем DHR26F;

- питание мезонина: от модуля;

- потребляемая мощность: не более 9,5 Вт.

Мезонин MIC1007-01 предназначен для организации обмена и контроля передачи информации по мультиплексному каналу информационного обмена (МКИО) по ГОСТ Р 52070-2003 (аналог MIL-STD-1553B). Мезонин имеет два независимых канала с резервированием. Каждый канал может выполнять функции контроллера шины (КШ), оконечного устройства (ОУ) или монитора (М0 – монитор шины и М1 – монитор по параметрам). Поддерживается все десять форматов сообщений.

Для связи мезонина с модулем используется интерфейс SPORT (для доступа к регистрам и данным протокола). Поддерживается режим DMA (память → SPORT TX, SPORT RX → память). В режиме КШ возможна настройка передачи цепочки сообщений.

Подключение к шине МКИО возможна как с трансформатором, так и без трансформаторное (прямое).

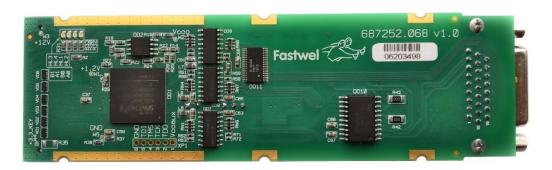

На рисунке 11 показан внешний вид мезонина MIC1007-01.

Рисунок 11 - Внешний вид мезонина МІС1007-01

Более подробная информация о мезонине в руководстве по эксплуатации ИМЕС.467451.014РЭ.

# 2.2.4 Мезонин интерфейса CAN MIC1010-01

#### Основные особенности:

- 4 поканально гальванически изолированных CAN2.0В интерфейса;

- обмен данными одновременно по 4-м каналам;

- настраиваемая скорость обмена до 1 Мбит/с;

- двойная буферизация передаваемых и принимаемых сообщений;

- размер пользовательских данных в сообщении до 8-ми байт;

- подключаемый терминатор линии для каждого канала;

- гальваническая изоляция, 1000 В;

- использование последовательного интерфейса SPORT для обмена данными с модулем-носителем;

- поддержка DMA транзакций;

- разъем подключения к шине DHR26F;

- программная совместимость с ОС Linux (не ниже v.3.19);

- питание: от модуля;

- мощность: не более 5 Вт.

Мезонин предназначен для осуществления операций ввода/вывода данных по шинам CAN в составе систем управления реального времени,

бортовых систем, средств безопасности и связи, контроля производства, высокоскоростного сбора данных и для других ответственных применений, предназначенных для работы в жестких условиях эксплуатации

Мезонин построен на основе микроконтроллера компании «Infineon», который содержит в себе процессорное ядро Cortex-M4 и Controller Area Network Controller (MultiCAN+).

Обмен между модулем и мезонином производится через два канала Universal Serial Interface Channel (USIC0), которые сконфигурированы для использования в качестве интерфейса SPORT. В свою очередь, в модуле для интерфейса SPORT реализована поддержка DMA, что позволяет минимизировать нагрузку на процессор вычислительной системы во время обмена данными с периферийными устройствами.

Для сопряжения каналов CAN с шинами и реализации физического уровня интерфейса используются приёмопередатчики компании «Analog Devices». Алгоритмы доступа к среде передачи и логика обработки сообщений (уровень Data Link Layer – подуровни Medium Access Control и Logic Link Control) реализуются в контроллере MultiCAN+ из состава микроконтроллера. Особенностью MultiCAN+ является полная аппаратная поддержка требований спецификации Bosch Controller Area Network Protocol Standard (Version 2.0).

Каждый канал имеет по два буфера размером 2048 байт — один на приём, другой на передачу. Скорость обмена в каждом из каналов может иметь любое значение вплоть до максимальной — 1 Мбит/с. Но при выборе скорости обмена необходимо помнить, что она обратно пропорциональна длине шины. При скорости 1 Мбит/с длина шины не может превышать 40 м, а для шины длиной 1000 м скорость обмена не может быть выше 50 кбит/с.

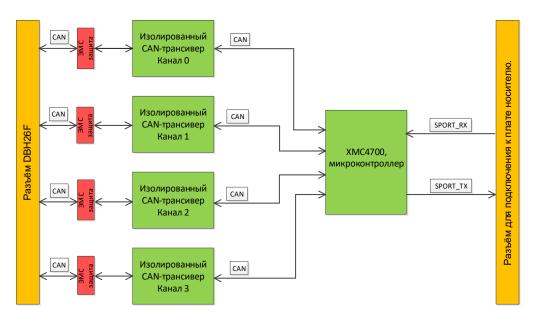

На рисунке 12 показана структурная схема мезонина.

Рисунок 12 - Структурная схема мезонина МІС1010-01

Для подключения CAN-портов мезонина к шинам предназначен разъём DBH26F. Выходные цепи каждого канала CAN гальванически изолированы от цепей других каналов и от остальных компонентов мезонина и модуля-носителя.

Рисунок 13 - Внешний вид мезонина МІС1010-01

#### 2.2.5 Мезонин интерфейсов RS485/422/232 MIC1011-01

Мезонин предназначен для осуществления операций ввода/вывода через 4 индивидуально гальванически изолированных последовательных порта типа RS485/RS422/RS232 и представляет собой плату преобразования уровней сигнала от UART, расположенного на модуле, в уровни сигналов соответствующих стандартов.

#### Основные особенности:

4 канала портов RS485/RS422/RS232;

- гальваническая изоляция каналов 750 В;

- защита выходных сигналов от электростатического разряда;

- подключение нагрузочного сопротивления 120 Ом для RS485;

- полная поддержка порта RS232 (9 pin) 1 канал;

- частичная поддержка порта RS232 (9 pin) 3 канала;

- полная поддержка порта RS485/RS422;

- возможность отключения питания каждого порта индивидуально;

- выходной разъем, установленный на мезонине DHR26F;

- программное переключение направления передачи для RS485.

- питание: от модуля.

- мощность: не более 4 Вт.

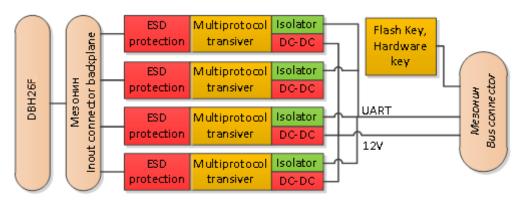

Структурная схема мезонина МІС1011-01 показана на рисунке 14.

Рисунок 14 - Структурная схема мезонина МІС1011-01

Внешний вид мезонина показан на рисунке 15.

Рисунок 15 - Внешний вид мезонина МІС1011-01

## 2.2.6 Мезонин интерфейса ПК МІС1012-0Х

#### Основные характеристики:

- 4 входных канала последовательного кода;

- от 2 до 4 выходных каналов последовательного кода;

- от 4 до 6 линий дискретного ввода/вывода разовые команды;

- выход РК обеспечивают выходной ток до 0.5А;

- скорость передачи информационных данных 12,5 кГц, 50 кГц, 100 кГц, с возможностью установить нестандартную частоты передачи от 768 Гц до 100 кГц;

- фильтрация слов в приемных каналах ПК по адресу (Label) параметра;

- гальваническая изоляция каналов: 750 В;

- выходной разъем DHR26F;

- питание: от модуля.

#### Варианты исполнения:

- МІС1012-01: 4 приемника, 2 передатчика, 6 разовых команд.

- МІС1012-02: 4 приемника, 4 передатчика, 4 разовых команд.

Мезонин интерфейса последовательного кода (ПК) и разовых команд (РК) (последовательный код ГОСТ 18977-79 и РТМ1495-75 с изм.3 (аналог ARINC 429), и разовые команды ГОСТ 18977-79) предоставляет разработчикам доступ к линиям приема ПК, передачи ПК и линиям РК работающим на вход или выход. Линии ПК и РК гальванически развязаны от цифровой части.

Для связи мезонина MIC1012 с модулем используется интерфейс SPORT (для доступа к регистрам и данным протокола). Поддерживается режим DMA (память → SPORT TX, SPORT RX → память).

Внешний вид мезонина МІС1012 показан на рисунке 16.

Рисунок 16 - Внешний вид мезонина МІС1012

Более подробная информация в эксплуатационной документации на мезонин ИМЕС.467451.019РЭ.

#### 2.2.7 Описание разъемов мезонинов и портов модуля

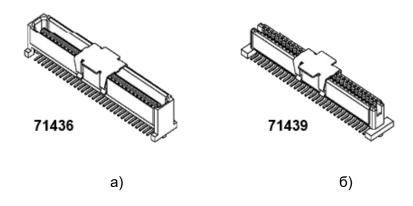

Межплатные соединения модуля и мезонинов осуществляются разъемами типа 71436 (на модуле) и 71439 (Molex) (на мезонине) (рисунок 17). Содержит 64 контакта с максимальным током нагрузки 0,5 A (предельный 1 A) и напряжением изоляции 250 B AC на контакт.

Рисунок 17 - Разъемы МОLEX 71436 (а) и 71439 (б)

Таблица 7 – Описание 64 контактного разъема для подключения мезонинов

| Nº       | Name pin               | Параллельный<br>порт     | UART и Timer                                                           | SPI и SPORT                        | 32 разрядная<br>шина Wishbone |  |  |

|----------|------------------------|--------------------------|------------------------------------------------------------------------|------------------------------------|-------------------------------|--|--|

| 1        | GND                    | Земля сигнальная         |                                                                        |                                    |                               |  |  |

| 2        | GND                    |                          |                                                                        |                                    |                               |  |  |

| 3        | +3V3                   | Питание интерф           | Питание интерфейсов. Используется ТОЛЬКО для питания идентификационной |                                    |                               |  |  |

| 4        | +3V3                   |                          |                                                                        | памяти                             |                               |  |  |

| 5        | CS_ID                  |                          |                                                                        | кационной памяти мезонина,         |                               |  |  |

| 6        | CLK_ID                 |                          |                                                                        | ичия модуля производиться п        |                               |  |  |

| 7        | SI_ID                  | путем определения        |                                                                        | а выводе SO_ID при подключ         | енном мезонине и              |  |  |

| 8        | SO_ID                  | IO D 0 0                 |                                                                        | ри его отсутствии.                 | D0                            |  |  |

| 9        | Port 0.0               | IO Reg0.0↔               | RX0←                                                                   | SPORT 0 CLK_TX↔                    | D0↔                           |  |  |

| 10<br>11 | Port 0.1               | IO Reg0.1↔               | TX0→ nRTS0→                                                            | SPORT 0 FRAME_TX↔ SPORT 0 TX →     | D1↔<br>D2↔                    |  |  |

| 12       | Port 0.2<br>Port 0.3   | IO Reg0.2↔               | nCTS0←                                                                 | SPORT 0 TX → SPORT 0 CLK RX↔       | D2↔<br>D3↔                    |  |  |

| 13       | Port 0.3               | IO Reg0.3↔               | nDTR0→                                                                 | SPORT 0 CLK_RX↔  SPORT 0 FRAME RX↔ | D3↔<br>D4↔                    |  |  |

| 14       | Port 0.5               | IO Reg0.4↔<br>IO Reg0.5↔ | nDSR0←                                                                 | SPORT 0 PRAIVIE_RX↔                | D5↔                           |  |  |

| 15       | Port 0.6               | IO Reg0.5↔               | nDCD0←                                                                 | SPORT 0 KX← SPORT 0 Limp→          | D5↔<br>D6↔                    |  |  |

| 16       | Port 0.7               | IO Reg0.7↔               | nRI0←                                                                  | 3PORT 0 LIIIIp→                    | D0↔<br>D7↔                    |  |  |

| 17       | Port 0.8               | IO Reg0.8↔               | RX1←                                                                   | SPORT 1 CLK TX↔                    | D8↔                           |  |  |

| 18       | Port 0.9               | IO Reg0.9↔               | TX1→                                                                   | SPORT 1 FRAME TX↔                  | D9↔                           |  |  |

| 19       | Port 0.10              | IO Reg0.9↔               | nRTS1→                                                                 | SPORT 1 TX →                       | D10↔                          |  |  |

| 20       | Port 0.11              | IO Reg0.10↔              | nCTS1←                                                                 | SPORT 1 CLK RX↔                    | D10↔<br>D11↔                  |  |  |

| 21       | Port 0.12              | IO Reg0.12↔              | nDTR1→                                                                 | SPORT 1 FRAME RX↔                  | D12↔                          |  |  |

| 22       | Port 0.13              | IO Reg0.13↔              | nDSR1←                                                                 | SPORT 1 RX←                        | D13↔                          |  |  |

| 23       | Port 0.14              | IO Reg0.14↔              | nDCD1←                                                                 | SPORT 1 Limp→                      | D14↔                          |  |  |

| 24       | Port 0.15              | IO Reg1.15↔              | nRI1←                                                                  | Of Orth 1 Emily 7                  | D15↔                          |  |  |

| 25       | Port 1.0               | IO Reg1.0↔               | RX2←                                                                   | SPI 0 MOSI→                        | D16↔                          |  |  |

| 26       | Port 1.1               | IO Reg1.1↔               | TX2→                                                                   | SPI 0 MISO←                        | D17↔                          |  |  |

| 27       | Port 1.2               | IO Reg1.2↔               | nRTS2→                                                                 | SPI 0 CLK →                        | D18↔                          |  |  |

| 28       | Port 1.3               | IO Reg1.3↔               | nCTS2←                                                                 | SPI 0 CS0→                         | D19↔                          |  |  |

| 29       | Port 1.4               | IO Reg1.4↔               | nDTR2→                                                                 | SPI 0 CS1→                         | D20↔                          |  |  |

| 30       | Port 1.5               | IO Reg1.5↔               | nDSR2←                                                                 | SPI 0 CS2→                         | D21↔                          |  |  |

| 31       | Port 1.6               | IO Reg1.6↔               | nDCD2←                                                                 | SPI 0 CS3→                         | D22↔                          |  |  |

| 32       | Port 1.7               | IO Reg1.7↔               | nRI2←                                                                  | SPI 0 CS4→                         | D23↔                          |  |  |

| 33       | Port 1.8               | IO Reg1.8↔               | RX3←                                                                   | SPI 1 MOSI→                        | D24↔                          |  |  |

| 34       | Port 1.9               | IO Reg1.9↔               | TX3→                                                                   | SPI 1 MISO←                        | D25↔                          |  |  |

| 35       | Port 1.10              | IO Reg1.10↔              | nRTS3→                                                                 | SPI 1 CLK →                        | D26↔                          |  |  |

| 36       | Port 1.11              | IO Reg1.11↔              | nCTS3                                                                  | SPI 1 CS0→                         | D27↔                          |  |  |

| 37       | Port 1.12              | IO Reg1.12↔              | nDTR3→                                                                 | SPI 1 CS1→                         | D28↔                          |  |  |

| 38       | Port 1.13              | IO Reg1.13↔              | nDSR3←                                                                 | SPI 1 CS2→                         | D29↔                          |  |  |

| 39       | Port 1.14              | IO Reg1.14↔              | nDCD3←                                                                 | SPI 1 CS3→                         | D30↔                          |  |  |

| 40       | Port 1.15              | IO Reg1.15↔              | nRI3←                                                                  | SPI 1 CS4→                         | D31↔                          |  |  |

| 41       | Port 2.0               | IO Reg2.0↔               |                                                                        | SPI 2 MOSI→                        | A0→                           |  |  |

| 42       | Port 2.1               | IO Reg2.1↔               |                                                                        | SPI 2 MISO←                        | A1→                           |  |  |

| 43       | Port 2.2               | IO Reg2.2↔               |                                                                        | SPI 2 CLK →                        | A2→                           |  |  |

| 44       | Port 2.3               | IO Reg2.3↔               |                                                                        | SPI 2 CS0→                         | A3→                           |  |  |

| 45       | Port 2.4               | IO Reg2.4↔               |                                                                        | SPI 2 CS1→                         | A4→                           |  |  |

| 46       | Port 2.5               | IO Reg2.5↔               |                                                                        | SPI 2 CS2→                         | A5→                           |  |  |

| 47       | Port 2.6               | IO Reg2.6↔               | T: 0.01.1T                                                             | SPI 2 CS3→                         | A6→                           |  |  |

| 48       | Port 2.7               | IO Reg2.7↔               | Timer0 OUT→                                                            | SPI 2 CS4→                         | A7→                           |  |  |

| 49       | Port 2.8               | IO Reg2.8↔               | Timer0 CLK←                                                            | SPI 3 MOSI→                        | SEL→                          |  |  |

| 50       | Port 2.10              | IO Reg2.9↔               | Timer0 GATE←                                                           | SPI 3 MISO←                        | WE→                           |  |  |

| 51       | Port 2.10              | IO Reg2.10↔              | Timer2 OUT→                                                            | SPI 3 CLK →                        | CLK→                          |  |  |

| 52<br>53 | Port 2.11<br>Port 2.12 | IO Reg2.11↔              | Timer2 CLK←<br>Timer2 GATE←                                            | SPI 3 CS0→<br>SPI 3 CS1→           | STB→<br>ACK←                  |  |  |

| 54       | Port 2.12<br>Port 2.13 | IO Reg2.12↔              | Timer2 GATE← Timer1 OUT→                                               | SPI 3 CS1→<br>SPI 3 CS2→           | ACK←<br>CYC→                  |  |  |

| ე4       | FUIL 2.13              | IO Reg2.13↔              | Tilliel LOUT→                                                          | 3F13 U3Z→                          | 010→                          |  |  |

| Nº | Name pin  | Параллельный<br>порт                                                 | UART и Timer       | SPI и SPORT                    | 32 разрядная<br>шина Wishbone |

|----|-----------|----------------------------------------------------------------------|--------------------|--------------------------------|-------------------------------|

| 55 | Port 2.14 | IO Reg2.14↔                                                          | Timer1 CLK←        | SPI 3 CS3→                     | INT0←                         |

| 56 | Port 2.15 | IO Reg2.15↔                                                          | Timer1 GATE←       | SPI 3 CS4→                     |                               |

| 57 | Strb0     | Strb0                                                                | OUT – выход тактов | ого счетчика 0 платы носител   | 19 →                          |

| 58 | Strb1     | Strb1 OUT – выход тактового счетчика 1 платы носителя →              |                    |                                |                               |

| 59 | +3.3V     | Дополнительное питание мезонина                                      |                    |                                |                               |

| 60 | +3.3V     |                                                                      |                    |                                |                               |

| 61 | +12V      |                                                                      |                    |                                |                               |

| 62 | +12V      | Питание мезонинов (для DC-DC гальванически развязанных частей схемы) |                    |                                |                               |

| 63 | GND       | 0                                                                    |                    |                                |                               |

| 64 | GND       |                                                                      | эемля преоо        | Земля преобразователей питания |                               |

# 2.2.8 Описание интерфейсов связи с мезонинами

# 2.2.8.1 Последовательны порт SPORT

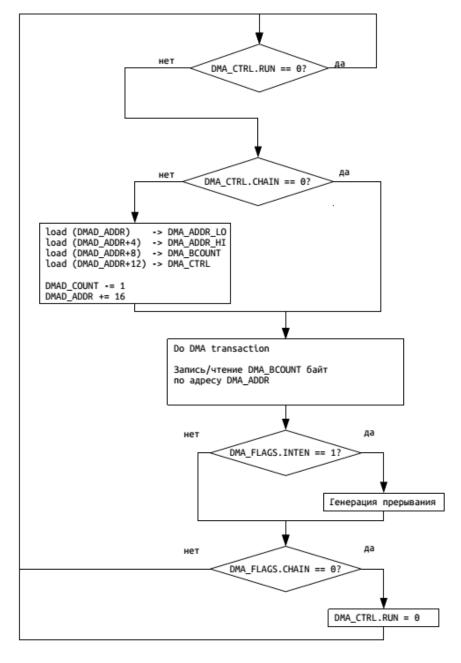

Последовательный порт SPORT представляет собой 32-х разрядный конфигурируемый мультискоростной последовательный порт с поддержкой DMA, TDM и I2S.

Порт обеспечивает интерфейс ввода-вывода (I/O) с различными периферийными устройствами. Каждый последовательный порт (Read, Write) имеет собственные регистры управления и буферы данных. Возможность использования различных вариантов тактовой и кадровой синхронизации позволяет поддерживать ряд протоколов обмена данными через последовательный порт и обеспечивать аппаратный интерфейс со многими преобразователями данных и кодеками промышленного стандарта.

Порт может работать на тактовой частоте до 32 МГц, поддерживая скорость передачи данных 32 Мбит/с. Возможность независимых приема и передачи данных обеспечивает значительную гибкость при организации коммуникаций. Данные последовательного порта могут автоматически передаваться во внутреннюю память и из нее с использованием режима передачи с прямым доступом к памяти (DMA – Direct Memory Access). Каждый последовательный порт поддерживает многоканальный режим с временным разделением каналов (TDM – Time Division Multiplexing).

Сигналы тактовой и кадровой синхронизации последовательного порта могут генерироваться внутри порта или приниматься от внешнего источника. Последовательный порт может работать с длиной слова от 3 до 32 бит и с различными форматами передачи данных: передача начинается со старшего бита или с младшего.

Последовательный порт имеет следующие характеристики:

независимые функции приема и передачи;

- передача слов данных длиной до 32 бит, начиная со старших бит или с младших бит;

- двойная буферизация данных в каждой части последовательного порта (и принимающей и передающей) имеется регистр данных, а также регистр сдвига; двойная буферизация сокращает время обслуживания последовательного порта;

- сигналы тактовой и кадровой синхронизации могут генерироваться внутри порта в широком диапазоне частот или приниматься от внешнего источника;

- управляемые прерываниями передачи одиночных слов данных во внутреннюю память и из нее;

- передачи по DMA во внутреннюю память и из нее каждый SPORT может автоматически принимать и/или передавать целый блок данных;

- цепочка операций DMA для передачи нескольких блоков данных;

- многоканальный режим с временным разделением каналов каждый SPORT может избирательно принимать данные из потока последовательно передаваемых бит с использованием временного разделения каналов.

## 2.2.8.2 Последовательный порт SPI

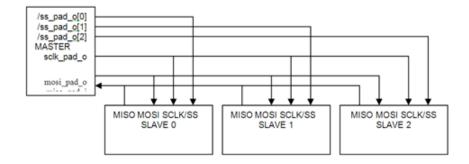

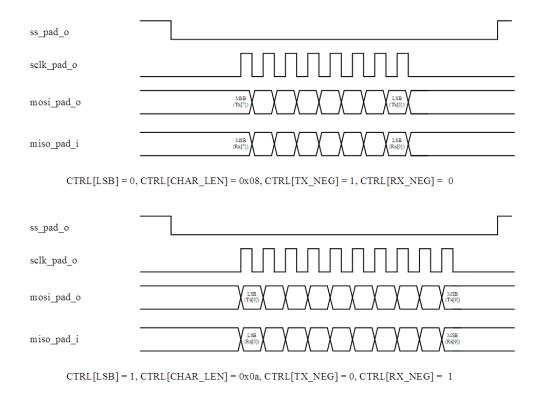

Последовательный порт SPI. Представляет собой 32-х разрядный конфигурируемый мультискоростной последовательный порт с поддержкой SPI 0 и SPI 3 протокола.

Последовательный порт имеет следующие характеристики:

- полнодуплексная передача данных;

- длинна передаваемого слова от 3 до 32 бит;

- передача может начинаться со старшего бита или с младшего;

- 4 линии выбора устройств;

- возможность использования прерывания при приеме/передаче данных;

- прием/передача данных по спаду/подъему тактового сигнала;

- частота тактирования до 32 МГц.

#### 2.2.8.3 Параллельный порт

Представляет собой 16-ти разрядный параллельный порт с произвольным регистровым доступом на ввод/вывод, без использования FIFO. Параллельный порт имеет следующие характеристики:

- разрядность порта 16 бит;

- раздельное конфигурирование битов порта на ввод/вывод;

- аппаратный формирователь импульсов, подключаемый к каждому биту порта;

- генерация прерываний при изменении состояния входных данных порта.

## 2.2.8.4 Таймер

Представляет собой модифицированный таймер типа 8254. Таймер имеет следующие характеристики:

- тактовая частота 20 МГц;

- максимальная внешняя тактовая частота 32 МГц;

- разрядность таймера 32 бита;

- режимы работы 0 5 аналогичны режимам таймера 8254;

- доступ к регистрам 32-х разрядный;

- возможность внешнего запуска таймера;

- возможность каскадирования таймеров;

- наличие двух 32-х разрядных делителей частоты для выработки импульсов.

#### 2.2.8.5 UART 16550A

Программная и аппаратная эмуляция функционала чипа 16550A. Дополнительные данные http://ru.wikipedia.org/wiki/16550\_UART.

## 2.2.8.6 Идентификатор мезонина модуля-носителя

Представляет собой микропрограммный автомат для автоматического считывания конфигурационной информации об установленном мезонине, по протоколу SPI, при подаче питания на мезонин. Для чтения информация доступна в соответствующем банке памяти модуля и используется для конфигурирования интерфейсов связи с мезонинами для работы с конкретным мезонином. Также существует, интерфейс произвольного доступа к микросхеме идентификационной памяти, предназначенный для программирования памяти в условиях производственного цикла, а также для возможности доступа к специфически данным конкретного мезонина, например, калибровочных констант.

# 2.3 Карта памяти модуля

На системной шине PCI модуль DIC552 определяется как «**System peripheral**» с VID:PID **1D8C:D80B.** Модуль DIC553 определяется как два устройства «**System peripheral**» с VID:PID **1D8C:D80B.**

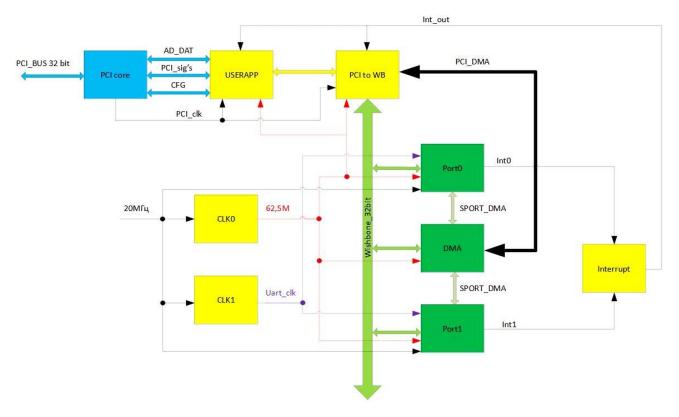

Обобщенная структура конфигурации FPGA показана на рисунке 18.

Рисунок 18 - Обобщенная структура конфигурации FPGA

#### Основные компоненты:

- PCI core IP ядро (LogiCORE IP Initiator/Target v4.14) ф. Xilinx;

- USERAPP блок формирующий логику обмена в режиме Target и Initiator PCI (набор автоматов), преобразования сигналов от IP ядра и пользовательского ПО:

- PCI to WB блок формирующий внутреннюю шину Wishbone, а так же переход от внутренней частоты обработки к частоте шины PCI;

- CLK0 и CLK1 блок формирующие внутренние частоты синхронизации: 62,2 МГц (вся интерфейсная и внутренняя обработка), и 18,519 МГц (частота UART);

- DMA блок формирующий DMA обмен на шине PCI;

- Port0, Port1 блок, формирующие все интерфейсы.

- Interrupt блок формирующий прерывания

На рисунке 19 показана обобщенная структура блока Port0 и Port1.

Рисунок 19 - Обобщенная структура блока Port

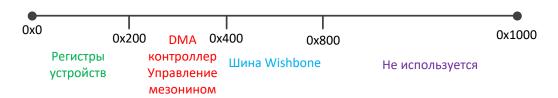

Пространство ввода-вывода модуля образовано 4-мя банками регистров: два банка регистров портов управления мезонинами (Port 0 и Port1) – банк 0 и 1; порт состояния и управления блоком прямого доступа к памяти (DMA module) – банк 2; регистры служебной информации шины PCI – скрыты от пользователя. В качестве внутренней межмодульной шины FPGA изделия использована параллельная шина Wishbone. Прерывания от всех устройств ввода-вывода объединены по логическому «ИЛИ». Обнаружение источника прерывания осуществляется программными средствами, путем последовательного чтения регистров состояния устройств ввода-вывода размещенных в FPGA.

Внутренняя частота синхронизации – 62,5 МГц, которая формируется от высокостабильного генератора с малым джиттером частотой 20 МГц.

Для согласования тактирования внутренней шины Wishbone (62,5 МГц) с частотой синхронизации системной шины PCI (до 33 МГц) служит блок PCI to WB.

Карта памяти представляет собой область из двух банков памяти (ВАК в области РСІ устройства). Банк памяти 0 и 1 отвечают за доступ к интерфейсам связи с мезонинами 0 (Port0) и 1 (Port1), соответственно. Они идентичны по расположению регистров и отличаются только базовым адресом. В каждом банке памяти находится статический набор регистров, позволяющий осуществлять доступ ко всем интерфейсам FPGA, вне зависимости от типа установленного мезонина. На рисунке 20 приведена модель пространства ввода-вывода и карта банка памяти, обслуживающего один мезонин, относительно базового адреса (таблица 8). Полный объем каждого банка памяти 4 кБ.

Рисунок 20 - Модель пространства ввода-вывода мезонина

#### Таблица 8

| Название и модулей          | Номер<br>прерывания | Адреса на шине | Номер<br>устройства |

|-----------------------------|---------------------|----------------|---------------------|

| Параллельный порт тип 1     |                     | 0x000 - 0x00C  | 0                   |

|                             |                     | 0x020 - 0x03C  | 1                   |

| Параллельный порт тип 2     | 0                   | 0x040 - 0x05C  |                     |

| Интерфейс идентификации     |                     | 0x010 - 0x01C  |                     |

| мезонина                    |                     |                |                     |

| Последовательный порт тип   | 1                   | 0x080 - 0x09C  | 0                   |

| 1(SPI)                      | 2                   | 0x0A0 - 0x0BC  | 1                   |

| ·                           | 3                   | 0x0C0 - 0x0DC  | 2                   |

|                             | 4                   | 0x0E0 - 0x0FC  | 3                   |

| Последовательный порт тип 2 | 5                   | 0x100 - 0x11C  | 0                   |

| (SPORT). Передающий модуль  | 7                   | 0x140 - 0x15C  | 1                   |

| Последовательный порт тип 2 | 6                   | 0x120 - 0x13C  | 0                   |

| (SPORT). Приемный модуль.   | 8                   | 0x160 - 0x17C  | 1                   |

| Последовательный порт тип 3 | 9                   | 0x180 - 0x19C  | 0                   |

| (UART)                      | 10                  | 0x1A0 - 0x1BC  | 1                   |

|                             | 11                  | 0x1C0 - 0x1DC  | 2                   |

|                             | 12                  | 0x1E0 - 0x1FC  | 3                   |

| Модуль таймеров             | 13                  | 0x060 - 0x07C  |                     |

| Шина Wishbone (внешняя)     | 15                  | 0x400 - 0x7FC  |                     |

| Версия ПО                   |                     | 0x800          |                     |

## 2.3.1 Регистровая модель пространства ввода-вывода

# 2.3.1.1 Параллельный порт тип 1

Представляет собой регистровый цифровой ввод/вывод с возможностью задания направления. Дополнительно порт поддерживает возможность управления выходным коммутирующим блоком, осуществляющим подключение различных портов к выходным выводам FPGA. Базовый адрес на шине 0x000 (pport0) и 0x020 (pport1).

Таблица 9 - Карта памяти параллельного порта типа 1

| Адрес | Операция | Имя  | Описание                     |

|-------|----------|------|------------------------------|

| +0h   | R        | IN   | Входной регистр              |

| +0h   | W        | OUT  | Выходной регистр             |

| +4h   | R/W      | DIR  | Регистр направления          |

| +8h   | R/W      | MODE | Регистр коммутации устройств |

#### Таблица 10 - Входной регистр

| Бит   | Операция | Описание                    |  |

|-------|----------|-----------------------------|--|

| 15-0  | R        | Состояние входов 15-0 порта |  |

| 31-16 |          | Не используются             |  |

#### Таблица 11 - Выходной регистр

| Бит   | Операция | Описание                     |  |

|-------|----------|------------------------------|--|

| 15-0  | W        | Состояние выходов 15-0 порта |  |

| 31-16 |          | Не используются              |  |

#### Таблица 12 - Регистр направления

| Бит   | Операция | Описание                                                |

|-------|----------|---------------------------------------------------------|

| 15-0  | R/W      | 1 в соответствующем бите переводит порт на вывод данных |

| 31-16 |          | Не используются                                         |

#### Таблица 13 - Регистр коммутации устройств

| Бит   | Описание                                       |                                              |  |  |

|-------|------------------------------------------------|----------------------------------------------|--|--|

| 1-0   | 00                                             | К выводу 0 присоединено <u>устройство 0</u>  |  |  |

|       | 01                                             | К выводу 0 присоединено <u>устройство 1</u>  |  |  |

|       | 10 К выводу 0 присоединено <u>устройство 2</u> |                                              |  |  |

|       | 11 К выводу 0 присоединено <i>устройство</i> 3 |                                              |  |  |

|       |                                                |                                              |  |  |

| 31-30 | 00                                             | К выводу 15 присоединено <u>устройство 0</u> |  |  |

|       | 01                                             | К выводу 15 присоединено <u>устройство 1</u> |  |  |

|       | 10                                             | К выводу 15 присоединено <u>устройство 2</u> |  |  |

|       | 11                                             | К выводу 15 присоединено <u>устройство 3</u> |  |  |

## 2.3.1.2 Параллельный порт тип 2

Представляет собой регистровый цифровой ввод/вывод с возможностью задания направления. Порт может формировать прерывания при изменении состояния входных линий порта, а также генерировать одиночные импульсы положительной и отрицательной полярности заданной длительности на выходных линиях порта при записи логической 1 в соответствующий бит порта. Дополнительно порт поддерживает возможность управления выходным коммутирующим блоком, осуществляющим подключение различных портов к выходным выводам FPGA.

Базовый адрес на шине 0х040.

Таблица 14 - Карта памяти параллельного порта типа 1

| Адрес | Операция | Имя      | Описание                                      |

|-------|----------|----------|-----------------------------------------------|

| +0h   | R        | IN       | Входной регистр                               |

| +0h   | W        | OUT      | Выходной регистр                              |

| +4h   | R/W      | DIR      | Регистр направления                           |

| +8h   | R/W      | MODE     | Регистр коммутации устройств                  |

| +ch   | R/W      | GEN_MODE | Регистр управления импульсными выходами порта |

| +10h  | R/W      | GEN      | Регистр генерации импульсов                   |

| +14h  | R/W      | INT_EN   | Регистр управления прерываниями               |

| +18h  | R/W      | INT_R    | Регистр сброса прерываний                     |

| +1ch  | R/W      | WIDTH    | Регистр установки длительности импульса       |

#### Таблица 15 - Входной регистр

| Бит   | Операция | Описание                    |

|-------|----------|-----------------------------|

| 15-0  | R        | Состояние входов 15-0 порта |

| 31-16 |          | Не используются             |

#### Таблица 16 - Выходной регистр

| Бит   | Операция | Описание                     |  |

|-------|----------|------------------------------|--|

| 15-0  | W        | Состояние выходов 15-0 порта |  |

| 31-16 |          | Не используются              |  |

#### Таблица 17 - Регистр направления

| Бит   | Операция | Описание                                                |

|-------|----------|---------------------------------------------------------|

| 15-0  | R/W      | 1 в соответствующем бите переводит порт на вывод данных |

| 31-16 |          | Не используются                                         |

#### Таблица 18 - Регистр коммутации устройств

| Бит | Опис | Описание                               |  |  |

|-----|------|----------------------------------------|--|--|

| 1-0 | 00   | К выводу 0 присоединено устройство 0   |  |  |

|     | 01   | 1 К выводу 0 присоединено устройство 1 |  |  |

|     | 10   | ) К выводу 0 присоединено устройство 2 |  |  |

|     | 11   | К выводу 0 присоединено устройство 3   |  |  |

| Бит   | Опис | Описание                              |  |  |  |

|-------|------|---------------------------------------|--|--|--|

|       |      |                                       |  |  |  |

| 31-30 | 00   | К выводу 15 присоединено устройство 0 |  |  |  |

|       | 01   | К выводу 15 присоединено устройство 1 |  |  |  |

|       | 10   | К выводу 15 присоединено устройство 2 |  |  |  |

|       | 11   | К выводу 15 присоединено устройство 3 |  |  |  |

#### Таблица 19 - Регистр управления импульсными выходами порта

| Бит   | Операция | Описание                                                                                                                         |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------------|

| 15-0  | R/W      | Переключение выхода порта между выходным регистром и выходом генератора. 0 – подключен выходной регистр, 1 – выход генератора    |

| 31-16 | R/W      | к соответствующему выходу порта Полярность выходных импульсов: 0 — положительная, 1 — отрицательная для соответствующего выхода. |

## Таблица 20 - Регистр генерации импульсов

| Бит   | Операция | Описание                                                      |  |

|-------|----------|---------------------------------------------------------------|--|

| 15-0  | R/W      | Запись 1 в соответствующем бите приводит к генерации импульса |  |

|       |          | на выходе порта                                               |  |

| 31-16 |          | Не используются                                               |  |

#### Таблица 21 - Регистр управления прерываниями

| Бит   | Операция | Описание                                                 |  |

|-------|----------|----------------------------------------------------------|--|

| 1-0   | R/W      | 00 Прерывание по выводу 0 запрещено                      |  |

|       |          | 01 Прерывание по выводу 0 генерируется по положительному |  |

|       |          | фронту                                                   |  |

|       |          | 10 Прерывание по выводу 0 генерируется по отрицательному |  |

|       |          | фронту                                                   |  |

|       |          | 11 Прерывание по выводу 0 генерируется по любому фронту  |  |

|       | R/W      |                                                          |  |

| 31-30 | R/W      | То же для вывода 15                                      |  |

# Таблица 22 - Регистр сброса прерываний

| Бит   | Операция | Описание                                                        |

|-------|----------|-----------------------------------------------------------------|

| 15-0  | W        | Запись 1 в бит, соответствующий выводу порта, приводит к сбросу |

|       |          | прерывания на соответствующем выводе.                           |

| 15-0  | R        | Регистр состояния прерываний. 1 в соответствующем бите говорит  |

|       |          | о возникновении прерывания на соответствующем выводе порта.     |

| 31-16 |          | Не используются                                                 |

#### Таблица 23 - Регистр установки длительности импульса

| Бит  | Операция | Описание                                                      |

|------|----------|---------------------------------------------------------------|

| 7-0  | R/W      | Задает длительность импульса в периодах тактовой частоты шины |

|      |          | (20 нс) для выводов 3-0 порта.                                |

| 15-8 | R/W      | Задает длительность импульса в периодах тактовой частоты шины |

|      |          | (20 нс) для выводов 7-4 порта.                                |

| Бит   | Операция | Описание                                                      |

|-------|----------|---------------------------------------------------------------|

| 23-16 | R/W      | Задает длительность импульса в периодах тактовой частоты шины |

|       |          | (20 нс) для выводов 11-8 порта.                               |

| 31-24 | R/W      | Задает длительность импульса в периодах тактовой частоты шины |

|       |          | (20 нс) для выводов 15-12 порта.                              |

#### 2.3.1.3 Модуль работы с последовательной памятью

Модуль (flash\_key) производит все операции по доступу к микросхеме флэш-памяти, установленной на мезонине (soft key). Помимо работы с флэшпамятью, модуль также определяет наличие мезонина по поведению линии miso флэш-памяти при сбросе устройства. Условия – на мезонине линия miso должна быть подтянута к +3,3 В и на модуле установлена подтяжка 100 кОм к земле. Соответственно, при наличии установленного мезонина в 31 бите регистра состояния и управления флэш-памятью будет 1, в случае отсутствия 0. Установка мезонина проверяется один раз при подаче питания в течение 128 тактов (62,5 МГц) после сигнала сброса на шине РСІ. В течение времени проверки модуль вырабатывает дополнительный сигнал сброса предотвращения неправильного подключения модулей ввода-вывода К устройствам мезонина.

Адреса с 0x000 по 0xfff принадлежат системной области памяти, в которой расположены идентификаторы, требуемые для корректной работы драйверной подсистемы и идентификации мезонина.

```

fwm_DeviceId{

uuid_t product_uuid; - 16 байтный идентификатор типа мезонина.

uuid_t kernel_driver_uuid; - 16 байтный идентификатор драйвера ядра.

uuid_t user_driver_uuid; - 16 байтный идентификатор драйвера мезонина.

char serial_number_string[64]; - серийный номер мезонина

char vendor_string[32]; - reserved

char product_string[32]; - reserved

uint32_t hw_version; - требуемая версия библиотеки hardware.

uint32_t sw_version; - требуемая версия библиотеки software.

char extra_data[128]; - reserved

uint32_t crc; - контрольная сумма

};

```

Начиная с адреса 0x1000, находится пространство, которое может быть использовано в пользовательских целях.

Таблица 24 - Регистр состояния и управления флэш-памятью (адрес на шине 0х010)

| Бит   | Операция | Описание                                                                                                  |                    |                   |

|-------|----------|-----------------------------------------------------------------------------------------------------------|--------------------|-------------------|

| 0-7   | W        | Данные, записываемые в память (1 байт)                                                                    |                    |                   |

| 0-7   | R        | Данные, считанные из памяти (1 байт)                                                                      |                    |                   |

| 23-8  | R/W      | Адрес, по которому производится                                                                           | я операция чтения  | /записи (16 бит). |

|       |          | Тип микросхемы памяти                                                                                     | Максимальный а     | адрес             |

|       |          | 25080                                                                                                     | 0x3ff              |                   |

|       |          | 25160                                                                                                     | 0x7ff              |                   |

|       |          | 25320                                                                                                     | 0xfff              |                   |

|       |          | 25640                                                                                                     | 0x1fff             |                   |

|       |          | 25128                                                                                                     | 0x3fff             |                   |

|       |          | 25256                                                                                                     | 0x7fff             |                   |

| 00.04 | DAM      | 16                                                                                                        |                    |                   |

| 26-24 | R/W      | Команда, выполняемая микросхе                                                                             | емои памяти        | 16                |

|       |          | Команда                                                                                                   |                    | Код               |

|       |          | Разрешение записи                                                                                         |                    | 0b110             |

|       |          | Запрет записи                                                                                             |                    | 0b100             |

|       |          | Чтение регистра состояния                                                                                 |                    | 0b101             |

|       |          | Запись регистра состояния       0b001         Чтение данных       0b011         Запись данных       0b010 |                    | 1                 |